Основні елементи цифрової мікропроцесорної техніки

Напівпровідникові запам'ятовувальні пристрої

4.1 Елементи мікропроцесорної техніки

Тригери Інтегральні тригери зазвичай реалізуються на логічних елементах І-НЕ, АБО-НЕ. Тригер призначений для зберігання значення однієї логічної змінної (або значення однорозрядного двійкового числа; при зберіганні багаторозрядних двійкових чисел для запам'ятовування значення кожного розряду числа використовуються окремий тригер). Відповідно до цього, тригер має два стани: одне з них позначається як стан 0, інше - як стан 1. Впливаючи на входи тригера, його встановлюють в потрібний стан.

Тригер має два виходи: прямий Q та інверсії-ний. Стан, в якому знаходиться тригер, визначається рівнями напруги на цих виходах: якщо напруга на виході Q відпо-яття рівню лог.0 (Q = 0), то приймається, що тригер знаходиться в стані 0, при Q = 1 тригер, знаходиться в стані 1. Логічний рівень на інверсному виходепредставляет собою інверсію перебуваючи-ня тригера (в стані 0 = 1, і навпаки).

Тригери мають різні типи входів. Їх позначення і призначення:

R (від англ. Reset) -роздільні вхід установки в стан 0;

S (від англ. Set) -роздільні вхід установки в стан 1;

К вхід установки універсального тригера у стан 0;

J - вхід установки універсального тригера у стан 1;

D (від англ. Delay) - інформаційний вхід установки тригера в стан, відповідне логічному рівню на цьому вході,

З-керуючий (синхронизирующий) вхід.

Найменування тригера визначається типами його входів. Напри-заходів, RS-тригер - тригер, який має входи типів R і S.

За характером реакції на вхідні сигнали тригери діляться на два типи: асинхронні і синхронні. В асинхронному тригері вхідні сигнали впливають на стан тригера безпосередньо з момен-ту їх подачі на входи, в синхронних тригерах - тільки при подачі синхронизирующего сигналу на керуючий вхід С.

асинхронні тригери

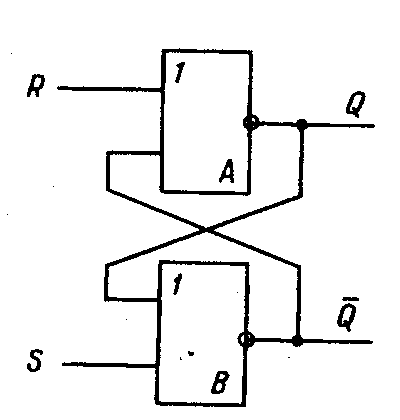

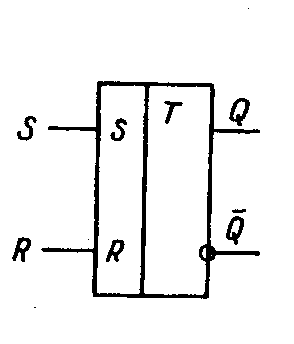

RS-тригер з прямими входами. Логічна структура тригера пред-ставлена на рис. 4.1а. Тригер побудований на двох логічних елементах АБО-НЕ, пов'язаних таким чином, що вихід кожного елемента під-укладений до одного з входів іншого. Таке поєднання елементів в пристрої можна встановлювати два стійких стану. Перемикання тригера з одного стійкого стану в інше відбувається при подачі активних сигналів на входи.

На рис. 4.2, б показано умовне обо-значення асинхронного RS-тригера.

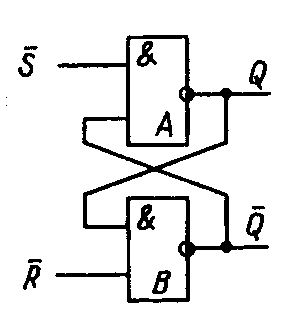

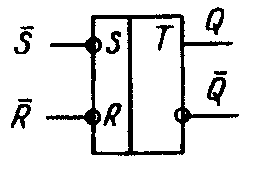

Rs-тригер з інверсними входами

Логічна структура тригера приведена на рис. 4.1, а. Відмінність від логічної структури розглянутого вище RS-тригера з прямими входами складається лише в тому, що тут використані логічні еле-менти І-НЕ. На рис. 4.2, б показано умовне позначення RS-тригера з інверсією-ними входами.

Синхронні тригери із статичним управлінням

Відмінність синхронного тригера від асинхронного полягає в тому, що синхронний тригер забезпечений додатковим входом, званим синхронизирующим (цей вхід часто називають також тактується входом). Призначення синхронизирующего входу в тому, щоб сигналом на цьому вході вирішувати прийом сигналів з інформаційних входів (входів, сигналами на яких проводиться перемикання тригера) в задані тимчасові інтервали. При відсутності сигналу на синхронно-зірующем вході інформаційні входи логічно відключаються і сигнали на цих входах не впливають на стан тригера.

Гідність синхронних тригерів полягає в тому, що вони по-зволяют усувати вплив відмінностей в значенні затримок в поширеною-неніі сигналу в окремих елементах схеми. При цьому забезпечується одночасний прийом сигналів різними частинами схеми в задані тимчасові відрізки.

Синхронні тригери, в свою чергу, діляться на два типи: синхронні тригери із статичним управлінням і синхронні тригери з динамічним управлінням. У перших тригери реагують на зміни сигналів на інформаційних входах, що відбуваються під час дії сигналу на синхронизирующем вході. Тому ці зміни допуску-ються тільки при відсутності сигналу на синхронизирующем вході. У синхронних тригерах з динамічним управлінням прийом сигналів з інформаційних входів відбувається протягом малої тривалості фронту (позитивного або негативного) сигналу на Сінхронізуется-ючий вході. В інший час інформаційні входи виявляються логічно відключеними і допускаються зміни сигналів на інфор-мационного входах і протягом дії синхронізуючого сигналу (виключаючи тривалість його фронту).

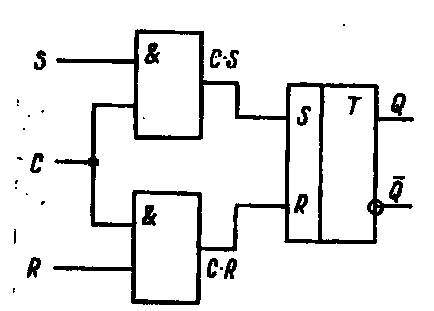

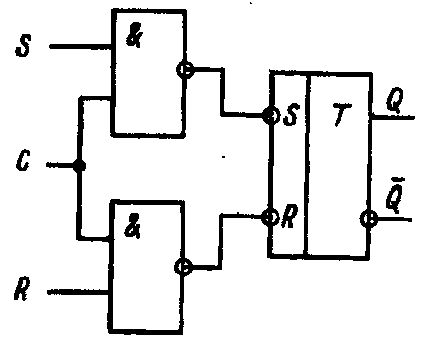

RS-тригер. На рис. 4.3а, б показані логічні структури синхрон-ного RS-тригера. Як видно з цих структур, синхронний RS-тригер складається з асинхронного тригера з прямими (або інверсними) вхо-дами, на входах R і S якого включені логічні елементи І (І-НЕ).

За допомогою логічних елементів І (І-НЕ) забезпечується передача активних логічних рівнів інформаційних входів S і R синхронного тригера на входи S і R входить до його складу асинхронні-ного тригера тільки при рівні лог. 1 на синхронизирующем вході С.

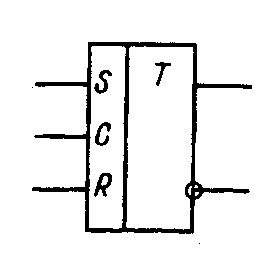

На рис. 4.3 в показано умовне позначення синхронного RS-тригера.

D-тригер. Цей тип тригера має лише один інформаційний вхід D. Вхід С - керуючий і служить для подачі синхронізується-ного сигналу.

Синхронні тригери, побудовані за принципом двоступеневого запам'ятовування інформації

Особливість тригерів з двоступінчастим запам'ятовуванням інформа-ції полягає в тому, що вони містять дві тригерні структури: одна з них утворює так званий провідний тригер, інша - ведений тригер. Обидва тригера функціонують як синхронні тригери із статичним управлінням.

Якщо на синхронизирующем вході С = 1, провідний тригер встановлюється в стан, відповідне сигналів, що надходять на інформаційні входи. Ведений тригер, який має інверсний синхронизирующий вхід, при цьому несприйнятливий до інформації, що надходить на його вхід з виходу ведучого тригера. Він продовжує перебувати в стані, в яке був раніше встановлений (в попередньому тактовом періоді).

При зміні значення С (з С = 1 на С = 0) провідний тригер відключається від інформаційних входів і перестає реагувати на зміни значень сигналів на цих входах; ведений тригер встановлюється в стан, в якому знаходиться провідний тригер. З цього моменту на входах встановлюються значення, відповідні вхідним сигналам, що надходять до моменту розглянутого фронту сигналу на синхронизирующем вході.

Управління процесами в тригері з двухступенча-тим запам'ятовуванням інформації за час тактового періоду здійснювала-вляется двома фронтами сигналу на синхронизирующем вході: на позитивному фронті відбувається установка провідного тригера, на негативному фронті - веденого тригера.