Контрольний розряд парності - студопедія

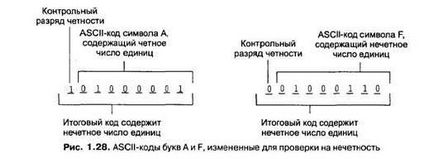

Простий метод виявлення помилок ґрунтується на тому принципі, що якщо відомо, що обробляється двійкового коду повинен містити непарне число одиниць, а отриманий код містить парне число одиниць, то сталася помилка. Для того щоб використовувати цей принцип, нам потрібна система, в якій кожен код містить непарне число одиниць. Цього легко досягти, додавши додатковий розряд, контрольний розряд відповідності (parity bit), на місце старшого розряду. (Отже, кожен 8-бітовий код ASCII стане 9-бітовим, а 16-бітової додатковий код стане 17-бітовим.) У кожному випадку ми присвоюємо цього розряду значення 1 або 0, так щоб весь код містив непарне число одиниць. Наприклад, ASCII-код літери А стає 101000001 (контрольний розряд парності 1), а код букви F стає 001000110 (контрольний розряд парності 0) (рис. 1.28). Хоча 8-бітовий код А містить парне число одиниць, а 8-бітовий код F - непарне, 9-бітовий код цих символів містить непарну кількість одиниць. Тепер, коли ми модифікувавши нашу систему кодування, код з парним числом одиниць буде означати, що сталася помилка і що обробляється двійковий код - неправильний.

Система контролю, описана вище, називається контролем непарності (odd parity), так як ми побудували нашу систему таким чином, що кожен код з-

тримає непарне число одиниць. Існує також метод-антипод - контроль парності (even parity). У таких системах кожен двійковий код містить парне число одиниць, і, отже, про помилку говорить поява коду з непарним числом одиниць.

Сьогодні використання контрольних розрядів парності в оперативній пам'яті комп'ютера досить поширене. Хоча ми говорили, що осередок пам'яті машин складається з восьми бітів, насправді вона складається з дев'яти бітів, один з яких використовується в якості контрольного біта. Кожен раз, коли 8-бітовий код передається в запоминающую схему, схема додає контрольний біт відповідності і зберігає виходить 9-бітовий код. Якщо код вже був отриманий, схема перевіряє його на парність. Якщо в ньому немає помилки, пам'ять прибирає контрольний біт і повертає 8-бітовий код. В іншому випадку пам'ять повертає вісім інформаційних бітів з попередженням про те, що повернутий код може не збігатися з вихідним кодом, поміщеним в пам'ять.

Довгі двійкові коди часто супроводжує набір контрольних бітів парності, які утворюють контрольний байт. Кожен розряд в байті відповідає певній послідовності бітів, що знаходиться в коді. Наприклад, один контрольний біт може відповідати кожному восьмому біту коду, починаючи з першого, а інший може відповідати кожному восьмому біту, починаючи з другого. У цьому випадку більша ймовірність виявити скупчення помилок в якійсь галузі вихідного коду, оскільки вони будуть знаходитися в області дії кількох контрольних бітів парності. Різновидом контрольного байта є такі схеми для виявлення помилок, як контрольна сума і циклічний надлишковий код.