Контролер переривань apic (advanced programmable interrupt controller) - інформатика,

5. Контролер переривань APIC (Advanced Programmable Interrupt Controller)

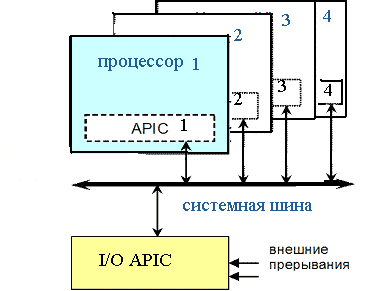

Система з APIC (рис.3.) Складається з локальних контролерів, встановлених в процесорах, і контролерів переривань (одного або декількох) від пристроїв введення / виводу. Завдання кожного локального контролера (Local APIC) - трансляція отриманих повідомлень в сигнали, що викликають все апаратні переривання свого процесора - маскуються (INTR), немасковані (NMI) і переривання системного обслуговування (SMI). Крім того, локальні APIC дозволяють кожному процесору генерувати переривання для інших процесорів. Локальний контролер має внутрішній інтервальний таймер, що дозволяє виробляти переривання через програмований інтервал часу.

Рис.3. Взаємодія вбудованого APIC і I / O APIC по системної шині

Контролер переривань від введення / виводу (I / O APIC) в мультипроцесорної режимі відповідає за розподіл переривань по процесорам, для чого може використовуватися статичне або динамічне розподіл. У разі статичного розподілу для кожного номера переривання вказується номер процесора, який його обслуговує. У разі динамічного розподілу кожне переривання направляється найменш пріоритетному в даний момент процесору. Цей же контролер відповідає за поширення сигналів про системні події (NMI, INIT, SMI) і міжпроцесорних переривань.

Вбудований в процесор програмований контролер переривань APIC розширює кількість раніше введених функцій контролера переривань. Вбудований APIC призначений для реєстрації переривань від джерел всередині процесора (наприклад, від блоку температурного контролю) або від зовнішнього контролера переривань і передачі їх ядру процесора на обробку. Особливо важлива роль покладається на вбудований APIC в багатопроцесорних системах, де APIC приймає і генерує повідомлення про міжпроцесорних переривання (IPI - InterProcessor Interrupt). Такі повідомлення можуть використовуватися для розподілу обробки переривань між процесорами або для виконання системних функцій (первісна завантаження, диспетчеризація задач і т.п.). Всі процесори багатопроцесорної системи приймають сигнали, вступники на вхід INTR # (масковані апаратні переривання). Біт IF в регістрі прапорів дозволяє заблокувати (замаскувати) обробку таких переривань. Сигнали переривань, що надходять на вход NMI #, є немаскіруемимі апаратними перериваннями немаскіруемое переривання НЕ блокуються прапором IF. Як ми вже знаємо, поки виконується програма - обробник немаскируемого переривання, процесор блокує отримання немаскованих переривань до виконання інструкції IRET, щоб виключити одночасну обробку декількох немаскованих переривань. Структура вбудованого APIC є архітектурним підмножиною мікросхеми контролера переривань Intel 82489.

Вбудований APIC розрізняє наступні джерела переривань:

1. Від локальних внутрішніх пристроїв. Сигнал запиту переривання надходить від пристрою, безпосередньо підключеного до сигналів LINT0 і LINT1 (наприклад, від контролера прериванійтіпа 8259A).

2. Від зовнішніх пристроїв. Сигнал запиту переривання від пристрою, підключеного до системного контролеру переривань.

3.Межпроцессорние (IPI). У багатопроцесорних системах один з процесорів може перервати інший за допомогою повідомлення IPI.

4. Від таймера APIC. Вбудований APIC містить таймер, який можна запрограмувати на генерацію переривання після досягнення певного відліку часу.

5. Від таймера монітора продуктивності. Сучасні процесори містять блок моніторингу продуктивності. Цей блок можна запрограмувати таким чином, щоб пов'язаний з ним таймер при досягненні певної відліку генерував переривання.

6. Від термодатчика. Сучасні процесори містять вбудований блок температурного контролю, який можна запрограмувати на генерацію переривань.

7. Внутрішні помилки APIC. Вбудований APIC може генерувати переривання при виникненні внутрішніх помилкових ситуацій (наприклад, при спробі звернутися до неіснуючого регістру APIC).

Джерела 1, 4, 5, 6, 7 вважаються локальними джерелами переривань і обслуговуються спеціальним набором регістрів APIC, званим таблицею локальних векторів (LVT - local vector table). Два інших джерела обробляються APIC через механізм повідомлень. Ці повідомлення, починаючи з процесора Pentium 4 передаються по системної шині, тому контролер переривань підключений безпосередньо до звичайного системного інтерфейсу (наприклад, до шини PCI). Наявність вбудованого APIC в процесорі виявляється за допомогою інструкції CPUID (1). Після сигналу RESET вбудований APIC включений, проте згодом він може бути відключений, тоді процесор буде працювати з перериваннями як Intel-386/486 (лінії LINT0 і LINT1 будуть використовуватися як NMI # і INTR #, до яких може бути підключений контролер переривань типу 8259A) .

Таблиця локальних векторів (LVT) складається з шести 32-бітових регістрів:

регістр вектора переривання від таймера;

регістр вектора переривання від термодатчика

регістр вектора переривання від монітора продуктивності

регістр вектора переривання LINT0;

регістр вектора переривання LINT1;

регістр вектора переривання помилки.

Значення в цих регістрах визначають:

номер вектора переривання;

тип переривання (fixed - переривання з зазначеним вектором, SMI - системне переривання, перехід в режим системного управління, NMI - немаскируемое переривання, INIT - скидання, ExtINT - зовнішнє переривання: при отриманні такого запиту на переривання процесор генерує цикл INTA і очікує номер вектора переривання від зовнішнього контролера;

маску переривання (переривання може бути замасковано).

Ці регістри також відображають стан переривання (доставляється це переривання ядру процесора в даний момент).

Крім того, APIC містить регістри управління таймером APIC, регістр версії, регістр помилки, регістри, пов'язані із обслуговуванням переривань (реєстр пріоритету, регістр запиту IRR, регістр обслуговування ISR), і регістри, пов'язані із передачею і прийомом IPI.

Контролер APIC в першу чергу призначений для симетричних мультіпроцесорних систем (SMP), описаних в документі Intel «MultiProcessor Specification» (MPS). Тут симетрія розглядається в двох аспектах:

симетрія пам'яті - все процесори користуються спільною пам'яттю, працюють з однією копією ОС;

симетрія введення / виведення - все процесори розділяють загальні пристрої введення / виводу і загальні контролери переривань.

Контролер I / O APIC є частиною чіпсета системної плати, наприклад, він входить в хаби ICH2 і ICH3 чіпсетів Intel. У спеціфкаціі MPS визначено три режими обробки переривань:

Режим PIC (PIC Mode) - емуляція пари PIC 8259A з традиційною передачею сигналів переривання одному процесору (завантажувального, BSP Bootstrap Pro cessor) по лініях INTR і NMI;

Ррежім роботи з подачею сигналів переривання по локальній шині APIC. При цьому I / O APIC може працювати спільно з PIC 8259A, забезпечуючи додаткові можливості (зокрема, додаткові входи запитів переривань);

Режим, коли переривання від пристроїв генерує I / O APIC; переривання можуть доставлятися будь-якому процесору; кожен вхід запиту індивідуально програмується за допомогою таблиці перенаправлення переривань (I / O Redirection Table).

Перші два режими забезпечують повну сумісність з системою переривань PC / AT, з програмної точки зору вони еквівалентні, відмінності лежать в області схемотехніки. За апаратному скиданню або при включенні харчування система починає працювати в одному із цих режимів. Коли система підготується до переходу в багатопроцесорний (MP) режим, APIC перекладається в симетричний режим і активізує таблицю перенаправлень переривань (попередньо програмно ініціалізувала).

В MP-системі є таблиця описів її компонентів. До системи переривань в цій таблиці відносяться описатели усіх I / O APIC, а також описатели призначень всіх використовуваних джерел переривань, пов'язаних з I / O APIC і локальними APIC. У описувач призначення для кожного джерела переривань вказується:

тип переривання: векторне з передачею вектора через APIC, векторне з зовнішньої передачею вектора (від PIC 8259A), NMI або SMI;

полярність сигналу і його тип (рівень або перепад);

ідентифікатор шини, на якій розташоване джерело;

ідентифікатор запиту на цій шині;

ідентифікатор і номер входу APIC, до якого підключений даний запит.

Для симетричних багатопроцесорних систем допустимі вектори в діапазоні 10h-FEh. Рівень пріоритету переривання визначається номером його вектора, діленим на 16. Найбільш пріоритетний рівень - нульовий.

Інформація про роботу «Організація переривань і прямого доступу до пам'яті в обчислювальних системах, розподіл ресурсів, технологія Plug and Play»