Комбінаційні цифрові пристрої 1

Мал. 15.8. Логічні елементи

Логічний елемент повинна бути реалізований у вигляді окремої інтегральної схеми. Часто інтегральна схема містить кілька логічних елементів.

Логічні елементи використовуються в пристроях цифрової електроніки (логічних пристроях) для виконання простого перетворення логічних сигналів.

Класифікація логічних елементів. Виділяються наступні класи логічних елементів (так звані логіки):

· Резисторно-транзисторна логіка (ТРЛ);

· Діод-транзисторна логіка (ДТЛ);

· Транзисторних-транзисторна логіка (ТТЛ);

· Емітерний-транзисторна логіка (ЕСЛ);

· Транзисторних-транзисторна логіка з діодами Шотткі (ТТЛШ);

· Логіка на базі МОП-транзисторів з каналами типу р (р -МДП);

· Логіка на базі МОП-транзисторів з каналами типу n (n -МДП);

· Логіка на базі комплементарних ключів на МДП-транзисторах (КМДП, КМОП);

· Інтегральна инжекционная логіка І 2 Л;

· Логіка на базі напівпровідника з арсеніду галію GaAs.

Сьогодні найбільш широко використовуються наступні логіки: ТТЛ, ТТЛШ, КМОП, ЕСЛ. Логічні елементи та інші цифрові електронні пристрої випускаються в складі серій мікросхем: ТТЛ - К155, КМ155, К133, КМ133; ТТЛШ - 530, КР531, КМ531, КР1531, 533, К555, Км555, одна тисяча п'ятсот тридцять три, КР1533; ЕСЛ - 100, К500, К1500; КМОП - 564, К561, тисячу п'ятсот шістьдесят чотири, КР1554; GaAs - К6500.

Найбільш важливі параметри логічних елементів:

· Швидкодія характеризується часом затримки поширення сигналу tзр і максимальної робочої частотою Fмакс. Час затримки прийнято визначати по перепадів рівнів 0,5Uвх і 0,5 # 916; U вих. Максимальна робоча частота Fмакс - ϶ᴛᴏ частота͵ при якій зберігається працездатність схеми.

· Здатність навантаження характеризується коефіцієнтом об'єднаю ?? ення по входу Коб (іноді використовують термін''коеффіціент об'єднаю ?? ення по виходу''). Величина Коб - ϶ᴛᴏ число логічних входів, величина Краз - максимальне число однотипних логічних елементів, які бувають підключені до виходу даного логічного елементу. Типові значення їх такі: Коб = 2 ... 8, Краз = 4 ... 10. Для елементів з підвищеною здатністю навантаження Краз = 20 ... 30.

· Перешкодостійкість в статичному режимі характеризується напругою Uпст. ĸᴏᴛᴏᴩᴏᴇ прийнято називати статичної помехоустойчивостью. Це таке максимально допустима напруга статичної перешкоди на вході, при якому ще не відбувається зміна вихідних рівнів логічного елемента.

· Потужність, споживана мікросхемою від джерела живлення. У разі якщо ця потужність різна для двох логічних станів, то часто вказують середню споживану потужність для цих станів.

· Вхідні порогові напруги високого і низького рівня Uвх.1порог і Uвх.0порог. відповідні зміни стану логічного елемента.

· Вихідні напруги високого і низького рівнів Uвих1 і Uвих0.

Використовуються й інші параметри.

Особливості логічних елементів різних логік. Для конкретної серії мікросхем характерно використання типового електронного вузла - базового логічного елемента. Цей елемент є основою побудови найрізноманітніших цифрових електронних пристроїв.

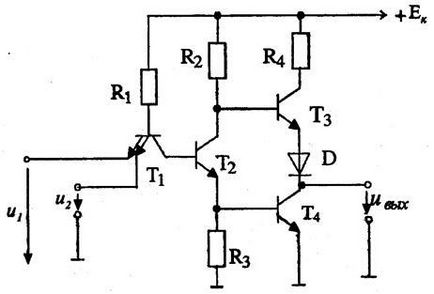

· Базовий елемент ТТЛ містить многоеміттерного транзистор, що виконує логічну операцію І, і складний інвертор (рис. 15.9).

Мал. 15.9. Базовий елемент ТТЛ

У разі якщо на один або обидва входи одночасно поданий низький рівень напруги, то многоемітттерний транзистор знаходиться в стані насичення і транзистор Т2 закритий, а отже, закритий і транзистор Т4. т. е. на виході буде високий рівень напруги. У разі якщо на обох входах одночасно діє високий рівень напруги, то транзистор Т2 відкривається і входить в режим насичення, що призводить до відкриття і насиченню транзистора Т4 і замикання транзистора Т3. ᴛ.ᴇ. реалізується функція І-НЕ. Для збільшення швидкодії елементів ТТЛ використовуються транзистори з діодами або транзисторами Шотткі.

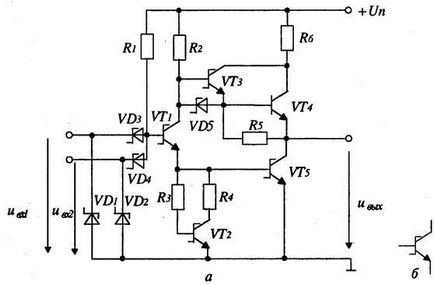

· Базовий логічний елемент ТТЛШ (на прикладі серії К555). В якості базового елементу серії мікросхем К555 використаний елемент

І-НЕ (рис. 15.10, а), а на рис. 15.10, б показано графічне зображення транзистора Шотткі.

Мал. 15.10. Логічний елемент ТТЛШ

Транзистор VT4 - звичайний біполярний транзистор.

· Напруга живлення +5 В;

· Вихідна напруга низького рівня не більше 0,4 В;

· Вихідна напруга високого рівня не менше 2,5 В;

· Стійкість - не менше 0,3 В;

· Середній час затримки поширення сигналу 20 нс;

· Максимальна робоча частота 25 МГц.

Особливості інших логік. Основою базового логічного елемента ЕСЛ є струмовий ключ, схема якого подібна до схеми диференціального підсилювача. Мікросхема ЕСЛ харчується негативним напругою (-4 В для серії К1500). Транзистори цієї мікросхеми не входять до режим насичення, що є однією з причин високої швидкодії елементів ЕСЛ.

У мікросхемах n -МОП і p -МОП використовуються ключі відповідно на МОП-транзисторах з n-каналами і динамічним навантаженням і на МОП-транзисторах з p-каналами. Для виключення споживання потужності логічним елементом в статичному стані використовуються комплементарні МДП-логічні елементи (КМДП або КМОП-логіка).

Логіка на базі напівпровідника з арсеніду галію GaAs характеризується найбільш високою швидкодією, що є наслідком високої рухливості електронів (в 3 ... 6 разів більше в порівнянні з кремнієм). Мікросхеми на базі GaAs можуть працювати на частотах порядку 10 ГГц.

Логічні пристрої поділяють на два класи: комбінаційні і послідовних.

Пристрій називають комбінаційною, в разі якщо його вихідні сигнали в певний момент часу однозначно визначаються вхідними сигналами, що мають місце в даний момент часу.

В іншому випадку пристрій називають послідовних або кінцевим автоматом (цифровим автоматом, автоматом з пам'яттю). У послідовних пристроях обов'язково є елементи пам'яті. Вихідні сигнали послідовних пристроїв визначаються не тільки сигналами, наявними на входах в даний момент часу, але і станом елементів пам'яті. Τᴀᴋᴎᴍ ᴏϬᴩᴀᴈᴏᴍ, реакція послідовних пристрою на определ ?? енние вхідні сигнали залежить від передісторії його роботи.

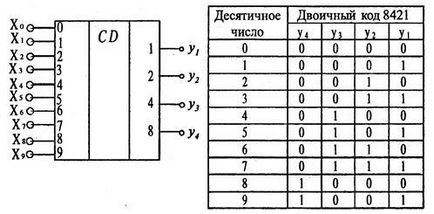

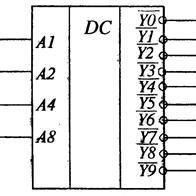

Шифратор - ϶ᴛᴏ комбінаційний пристрій, що перетворює десяткові числа в двійкову систему числення, причому кожному входу повинна бути поставлено у відповідність десяткове число, а набір вихідних логічних сигналів відповідає определ ?? енному двійкового коду. Число входів і виходів в повному шифраторі пов'язано співвідношенням n = 2 m. де n - число входів, m - число виходів. Шифратор для перетворення десятирозрядний одиничного коду (десяткових чисел від 0 до 9) в двійковий код. Умовне зображення такого шифратора і таблиця відповідності коду наведені на рис. 11.1. Використовуючи цю таблицю відповідності, запишемо логічні вирази, включаючи в логічну суму ті вхідні змінні, які відповідають одиниці деякої вихідної змінної. Так, на виході y1 буде логічна''1'' тоді, коли логічна''1'' буде або на вході Х1. або Х2. або Х5. або Х7. або Х9. ᴛ.ᴇ. в1 = Х1 + Х3 + Х5 + Х7 + Х9.

Мал. 16.1. Схема шифратора і таблиця відповідності коду

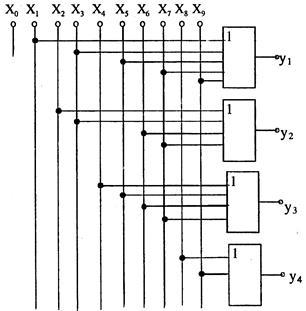

Уявімо на рис. 16.2 схему такого шифратора, використовуючи елементи АБО.

Мал. 16.2. Шифратор на логічних елементах АБО

У разі якщо на вс ?? ех входах - логічна одиниця, то на вс ?? ех висновках також логічна одиниця, що відповідає числу 0 в так званому інверсному коді (1111). У разі якщо хоча б на одному вході є логічний нуль, то стан вихідних сигналів визначається найбільшим номером входу, на якому є логічний нуль, і не залежить від сигналів на входах, що мають менший номер.

Основне призначення шифратора - перетворення номера джерела сигналу в код (наприклад, номери натиснутою кнопки деякої клавіатури).

Дешифратором прийнято називати комбінаційний пристрій, що перетворює n-розрядний двійковий код в логічний сигнал, що з'являється на тому виході,

десятковий номер якого відповідає бінарного колу. Число входів і виходів в так званому повному дешифраторі пов'язано співвідношенням m = 2 n. де n - число входів, а m - число виходів. У разі якщо в роботі дешифратора використовується неповне число виходів, то такий дешифратор прийнято називати неповним. Так, наприклад, дешифратор, який має 4 входи і 16 виходів, буде неповним, а якби виходів було тільки 10, то він був би повним.

Звернемося для прикладу до дешифратор К555ІД6 серії К555 (рис. 16.3).

Мал. 16.3. схема дешифратора

Дешифратор - одне з широко використовуваних логічних пристроїв. Його застосовують для побудови різних комбінаційних пристроїв. Шифратори і дешифратори є прикладами найпростіших перетворювачів ?? їй кодів.

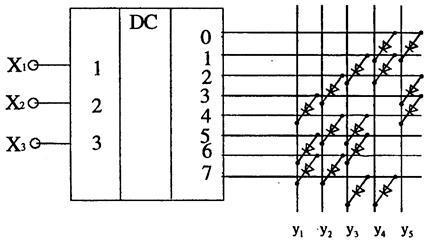

Перетворювачами кодів називають пристрої, призначені для перетворення одного коду в інший, при цьому часто вони виконують нестандартні перетворення кодів. Перетворювачі кодів позначають через X / Y.

Розглянемо особливості реалізації перетворювача на прикладі перетворювача Трьохелементний коду в пятіелементной за таблицею відповідності кодів, наведеної на рис. 16.4.

Мал. 16.4. Таблиця відповідності кодів для перетворювача кодів

Тут через N позначено десяткове число, відповідне вхідного двійкового коду. Перетворювачі кодів створюють за схемою дешифратор - шифратор.

Мал. 16.5. Схема перетворювача кодів

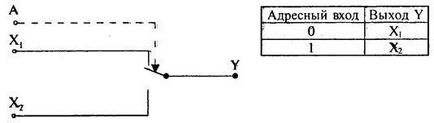

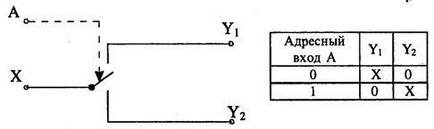

Розглянемо функціонування двухвходового мультиплексора (2 → 1), який умовно зображений у вигляді комутатора, а стан його входів Х1. Х2 і виходу Y наведено в таблиці (рис. 16.6).

Мал. 16.6. двовходовий мультиплексор

Виходячи з таблиці, можна записати наступне рівняння:

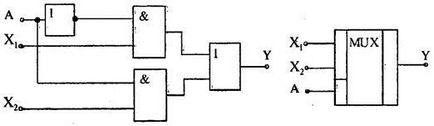

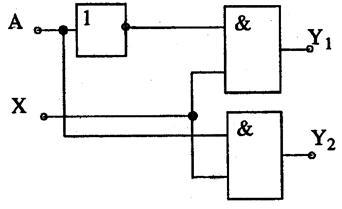

На рис. 16.7 показані реалізація такого пристрою і його умовне графічне позначення. Основою даної схеми є є дві схеми збігу на елементах І, які при логічному рівні''1'' на одному зі своїх входів повторюють на виході те, що є на іншому вході.

Мал. 16.7. Реалізація двухвходового мультиплексора

на логічних елементах І

Мультиплексори є універсальними логічними пристроями, на базі яких створюють різні комбінаційні і послідовних схема. Мультиплексори можуть використовувати в делителях частоти, тригерних пристроях, що зсувають пристроях, для перетворення паралельного двійкового коду в послідовний і ін.

Мал. 16.8. Функціональна схема демультиплексора з двома виходами

Розглянемо функціонування демультиплікатора з двома виходами, який умовно зображений у вигляді комутатора, а стан його входів приведено в таблиці (рис. 16.8). З цієї таблиці випливає:, ᴛ.ᴇ. реалізувати такий пристрій можна так, як показано на рис. 16.9.

Мал. 16.9. Реалізація демультиплексор з двома виходами

на логічних елементах І

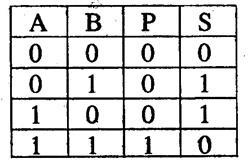

Суматори - ϶ᴛᴏ комбінаційні пристрої для складання чисел. Розглянемо додавання двох однорозрядних двійкових чисел, для чого складемо таблицю додавання (таблицю істинності), в якій відобразимо значення вхідних чисел А і В, значення результату підсумовування S і значення перенесення в старший розряд P (рис. 16.10). Робота пристрою, що реалізує таблицю істинності, описується наступними рівняннями:.

Очевидно, що по відношенню до колонку S реалізується логічна функція''ісключающее ІЛІ'', ᴛ.ᴇ. S = A B.

Мал. 16.10. Таблиця істинності

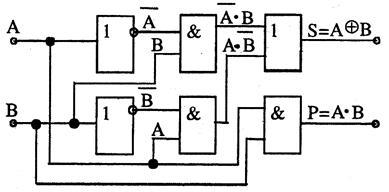

Пристрій, що реалізовує таблицю (рис. 16.10), називають полусумматора, і воно має логічну структуру, зображену на рис. 16.11. Оскільки полусумматор має тільки два входи, він може використовуватися для підсумовування лише в молодшому розряді.

Мал. 16.11. схема полусумматора

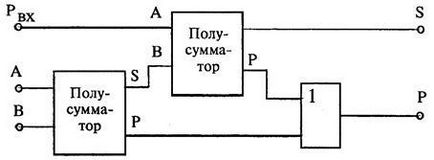

При підсумовуванні двох багаторозрядних чисел для кожного розряду (крім молодшого) вкрай важливо використовувати пристрій, що має додатковий вхід переносу.

Мал. 16.12. Схема повного суматора

Такий пристрій (рис. 16.12) називають повним суматором і його можна представити як об'єднаю ?? ення двох полусумматора (Рвх - додатковий вхід переносу).

Суматор позначають через SM.

Читайте також

4-1. Поняття комбінаційного цифрового пристрою, мікросхеми комбінаційного типу малому ступені інтеграції. Під комбінаційною цифровим пристроєм (КЦУ) розуміється цифровий пристрій, що забезпечує перетворення сукупності N вхідних цифрових сигналів в M. [читати далі].